#### CS 152: Computer Systems Architecture

#### **GPU** Computing Introduction

Sang-Woo Jun 2023

# The State of C

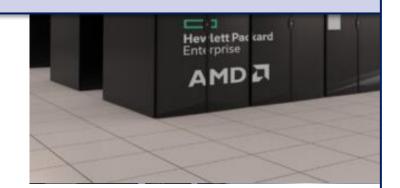

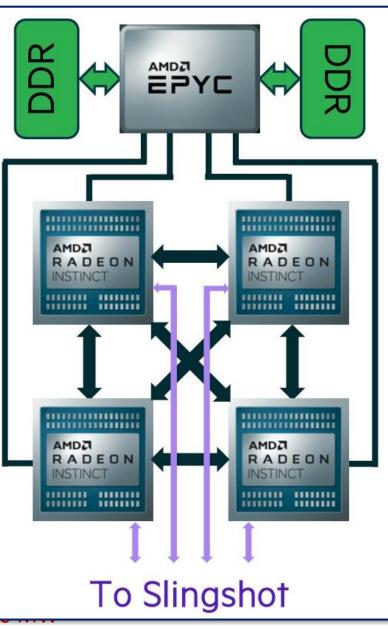

#### Department of Energy requested e

#### Heavy use of GPUs

1,000,000,000,000,000,000 floating p

Using 2016 technolog Using 2019 technolog, 20 MW

#### mtialeseerethcaneleseption to francisco

#### ded programming

#### 1**68/////**//

Image: TheNextPlatform (Calculated from "Electricity Consumption by County", California energy commission)

Lynn Freeny, Department of Energy

# Graphic Processing – Some History

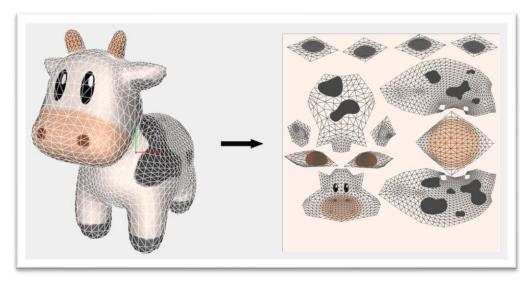

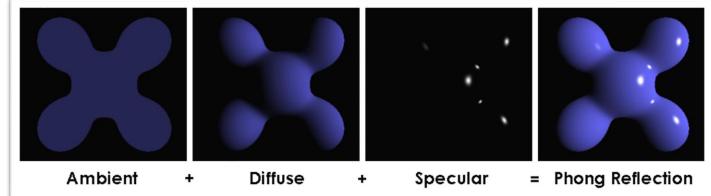

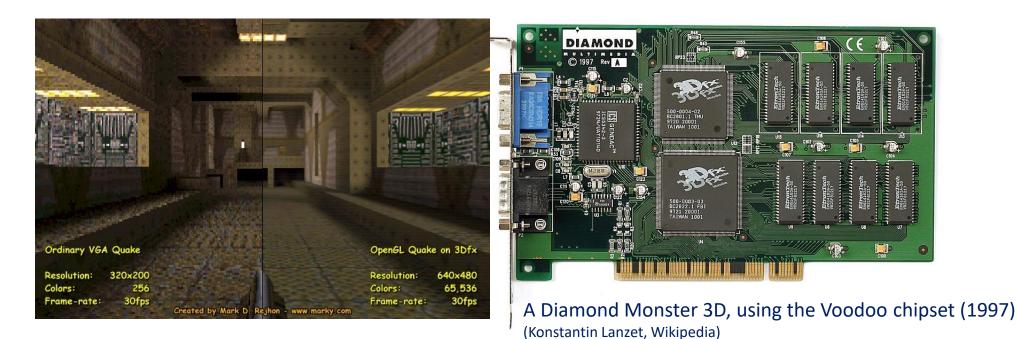

1990s: Real-time 3D rendering for video games were becoming common

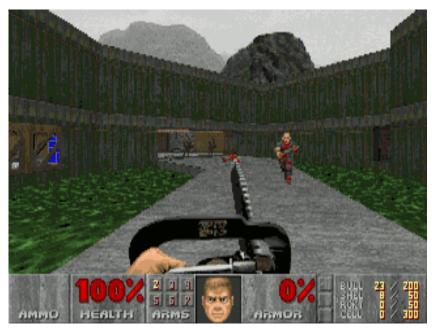

o Doom, Quake, Descent, ... (Nostalgia!)

□ 3D graphics processing is immensely computation-intensive

#### Texture mapping

Shading

Warren Moore, "Textures and Samplers in Metal," Metal by Example, 2014 Gray Olsen, "CSE 470 Assignment 3 Part 2 - Gourad/Phong Shading," grayolsen.com, 2018

# Graphic Processing – Some History

#### □ Before 3D accelerators (GPUs) were common

CPUs had to do all graphics computation, while maintaining framerate!

$\circ$   $\,$  Many tricks were played  $\,$

Doom (1993) : "Affine texture mapping"

- Linearly maps textures to screen location, disregarding depth

- Doom levels did not have slanted walls or ramps, to hide this

### Graphic Processing – Some History

#### □ Before 3D accelerators (GPUs) were common

CPUs had to do all graphics computation, while maintaining framerate!

Many tricks were played

Quake III arena (1999) : "Fast inverse square root" magic!

```

float Q_rsqrt( float number )

{

const float x2 = number * 0.5F;

const float threehalfs = 1.5F;

union {

float f;

uint32_t i;

} conv = {number}; // member 'f' set to value of 'number'.

conv.i = 0x5f3759df - ( conv.i >> 1 );

conv.f *= ( threehalfs - ( x2 * conv.f * conv.f ) );

return conv.f;

}

```

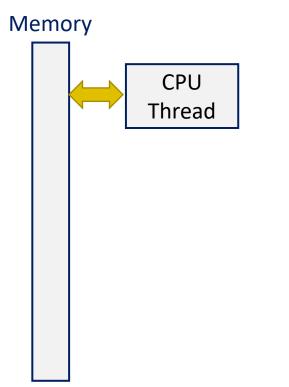

### Introduction of 3D Accelerator Cards

- Much of 3D processing is short algorithms repeated on a lot of data

pixels, polygons, textures, ...

- Dedicated accelerators with simple, massively parallel computation

Example: OpenGL Shader Language ("GLSL") Program a function, function runs for every single pixel on screen

A Diamond Monster 3D, using the Voodoo chipset (1997) (Konstantin Lanzet, Wikipedia)

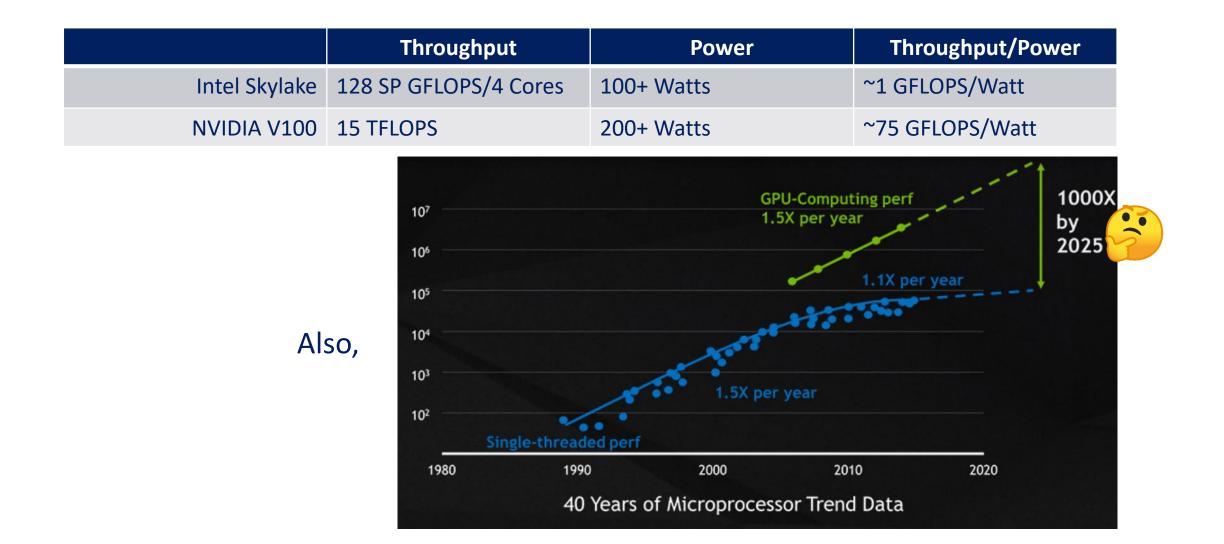

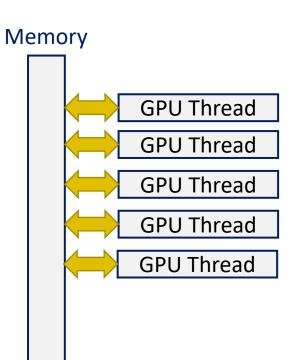

### Peak Performance vs. CPU

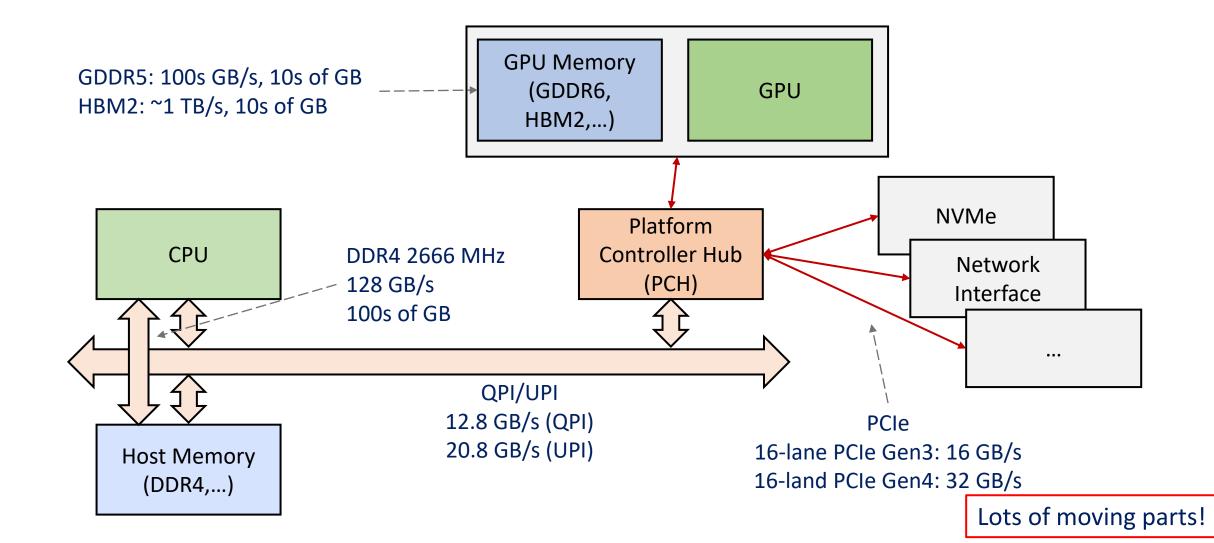

#### System Architecture Snapshot With a GPU

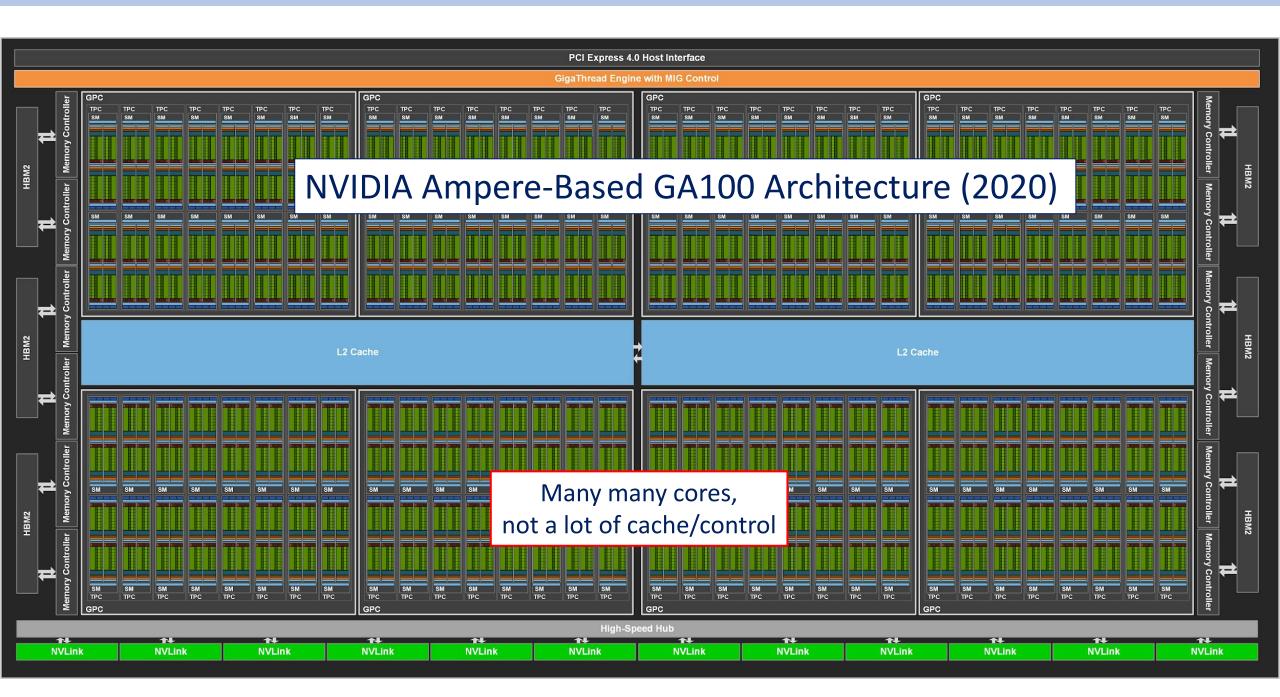

### Massively Parallel Architecture For Massively Parallel Workloads!

- □ NVIDIA CUDA (Compute Uniform Device Architecture) 2007

- $\circ$  A way to run custom programs on the massively parallel architecture!

- □ OpenCL specification released 2008

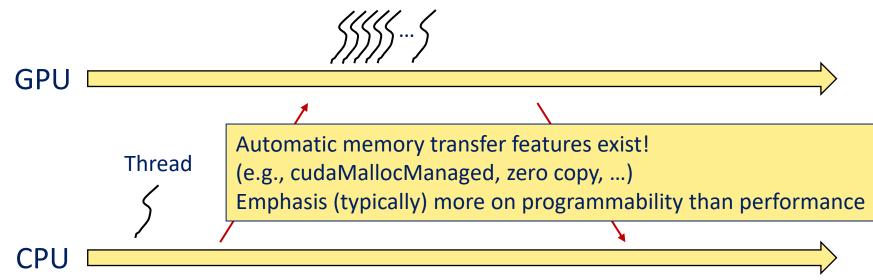

- Both platforms expose synchronous execution of a massive number of threads

GPU Threads

# High-Performance Graphics Memory

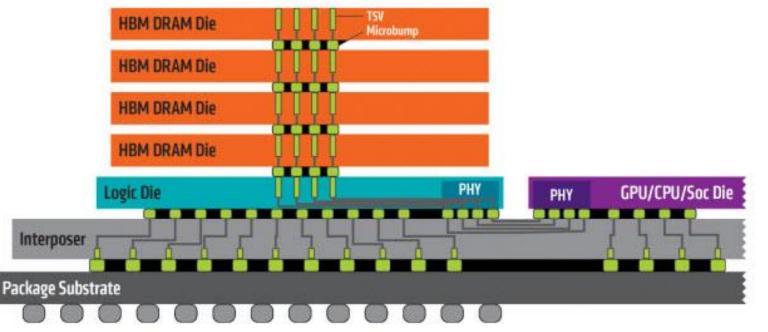

□ Modern GPUs even employing 3D-stacked memory via silicon interposer

• Very wide bus, very high bandwidth to feed many, many cores

o e.g., HBM2 in Volta, Ampere

Graphics Card Hub, "GDDR5 vs GDDR5X vs HBM vs HBM2 vs GDDR6 Memory Comparison," 2019

#### The Hardware Lottery Sarah Hooker Communications of The ACM, 2021

### Hardware Lottery Winners: General-Purpose CPU Threads

- □ Moore's Law + Dennard Scaling = Dependable performance scaling

- Faster general-purpose hardware available next year

- Why risk uncertain reward with specialized designs?!

- □ Resources focused on making general purpose CPUs faster

### Hardware Lottery Winners: General-Purpose CPU Threads

#### □ Von-Neumann general-purpose CPUs

- $\circ$   $\,$  Not very good with parallel execution

- Not much emphasis on memory bandwidth

- □ Efficient with branch-heavy expert systems

- Favors symbolic approaches to AI (LISP, Prolog)

- □ Inefficient with massively parallel matrix multiplication

- Disfavors neural networks

### Hardware Lottery Losers: Neural Nets and the AI Winter

- □ "The lost decades", or the "AI Winter"

- $\circ~$  Research predominantly focused on symbolic approaches

- Insufficient hardware capacity to train realistic neural nets

- □ NN theory was already available

- Backpropagation (1963, reinvented in 1976, and again in 1988)

- Deep convolutional neural networks (1979, paired with backpropagation in 1989)

- $\circ~$  Need for parallel architectures and memory already noticed in 1980

- □ But... already lost the hardware lottery

### Hardware Lottery Losers: Neural Nets and the AI Winter

- □ Ventures into specialized hardware for NN existed

- o e.g., "Connection Machine" (pictured), 1985

- But none reached critical mass

- $\circ$  Fractured ISA, programming model

- No application -> No customers -> No research -> No application...

#### New Hardware Lottery Winners: GPUs

□ A "fluke" in the 2000s enabled neural networks

- GPUs originally designed for gaming

- Massively parallel, a program for each pixel (for example)

- Re-purposed for training!

### CNNs and GPUs – Perfect Match

Two papers using CNNs to identifying cats

"Building High-Level Features Using Large Scale Unsupervised Learning"

16,000 CPU cores

o **2012**

- □ "Deep learning with COTS HPC systems"

- $\circ~$  Two CPU cores and two GPUs

- o **2013**

What other ideas are we missing due to the hardware lottery?

### Yet Another Lottery Winners: Specialized Hardware

- CNNs have reached critical mass, won the hardware lottery (finally)

- $\circ~$  Hardware is optimizing for CNNs

- Tensor cores in GPUs, bfloat units in CPUs, TPUs, ...

- Quantized arithmetic, unstructured pruning, etc making way into hardware

- □ Specialized hardware enables ever-larger models

- $\circ~$  The baseline models are becoming very deep, very large

### Yet Another Lottery Losers: Non-CNN Models

- But, other ideas have lost the lottery

- $\circ~$  If an alternative algorithm is as complex as CNNs but not trainable with TPUs

- Not feasible to train!

- $\circ~$  Imagine training a modern NN without GPUs

- Example: "Capsule Networks" (2019)

- o "include novel components like squashing operations and routing by agreement."

- "aimed to solve for key deficiencies in convolutional neural networks (lack of rotational invariance and spatial hierarchy understanding)"

- "but strayed from the typical architecture of neural networks as a sequence of matrix multiplies."

#### Yet Another Lottery Losers: Non-CNN Models

□ Are capsule nets the future? Maybe, maybe not!

But, researchers will gravitate towards models/algorithms well-suited for GPU/TPU/Matrix multiply.

$\circ~$  And away from those unsupported

□ What great ideas are we missing because they lost the hardware lottery?

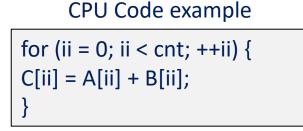

#### Back to CUDA...

What is the programming interface? 1000 programs for 1000 threads?

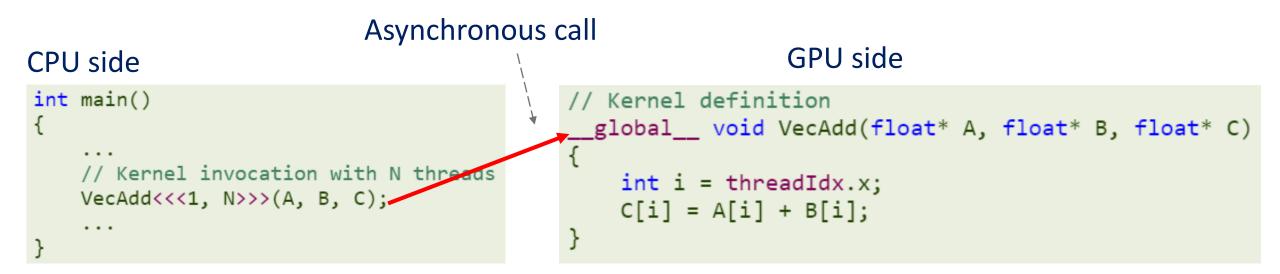

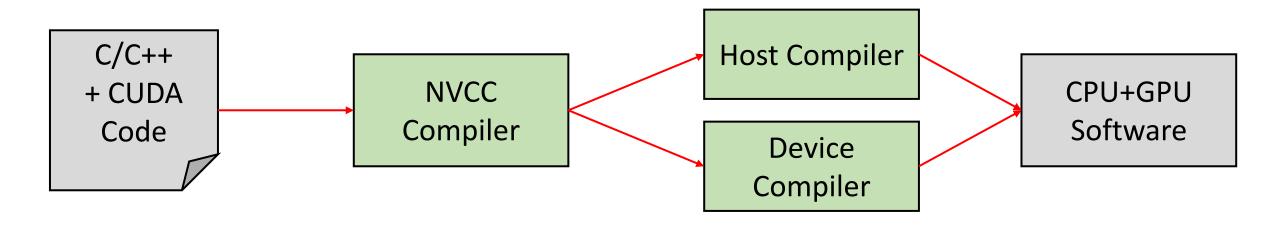

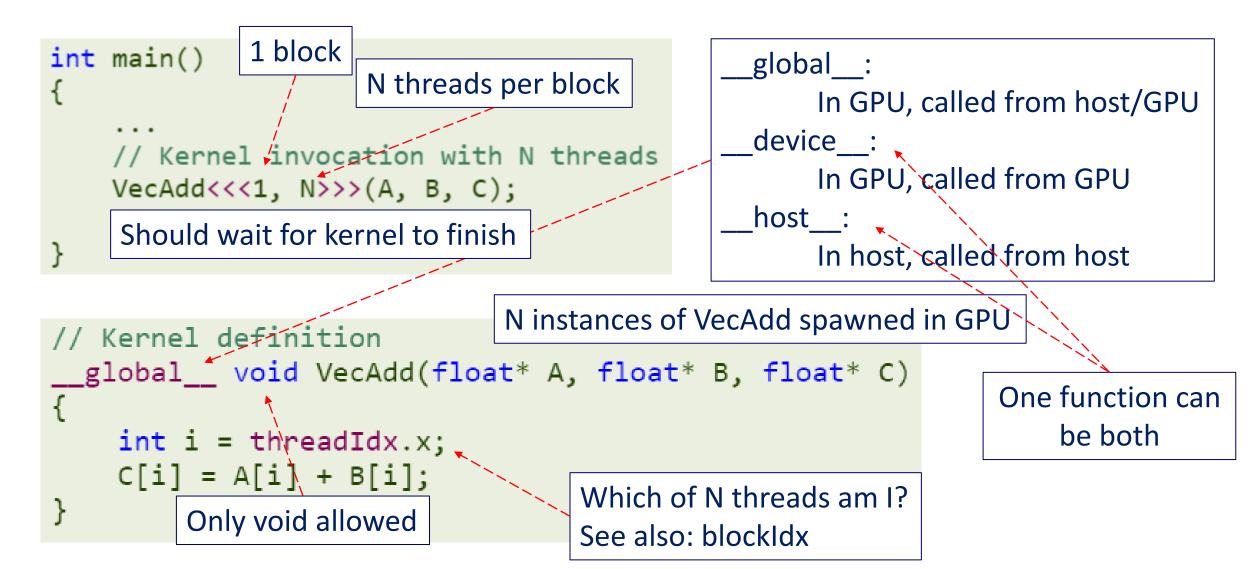

# GPU programming abstraction

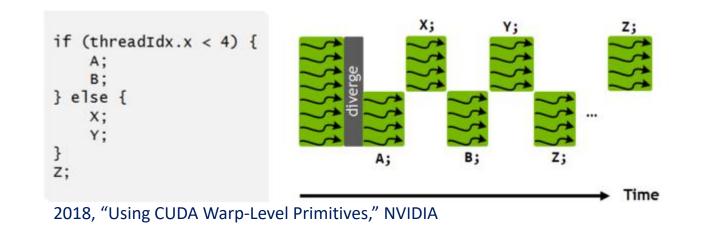

□ "SIMT" (Single Instruction Multiple Threads), introduced by NVIDIA

- Simply put: Identical program ("Kernel") executed on multiple threads

- Thread ID is given as a parameter to the program,

so each thread can perform different work despite identical code

- $\circ~$  Another kernel parameter is "block size", the number of threads to use

GPU Code example

```

__global___void KernelFunction(...) {

int tid = threadIdx.x;

int blocksize = ceiling(cnt/blockDim.x);

for (i = 0; i < blocksize; ++i) {

int ii = blocksize*tid+i;

if ( ii < cnt ) C[ii] = A[ii] + B[ii];

}

}</pre>

```

Thread dimensions given as part of request from host software

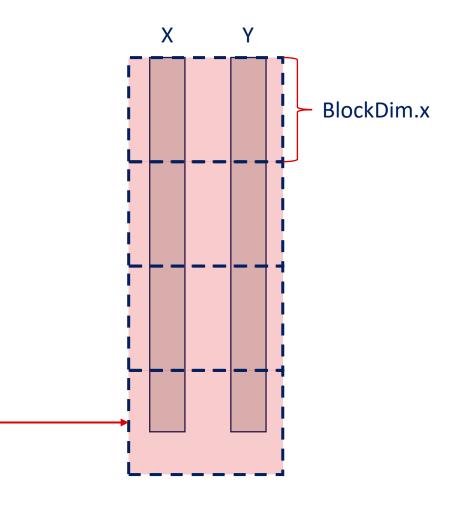

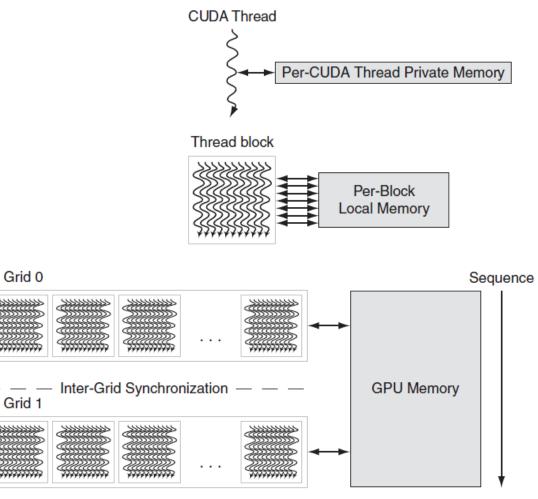

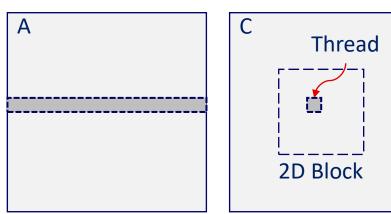

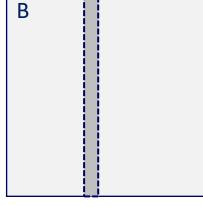

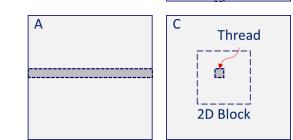

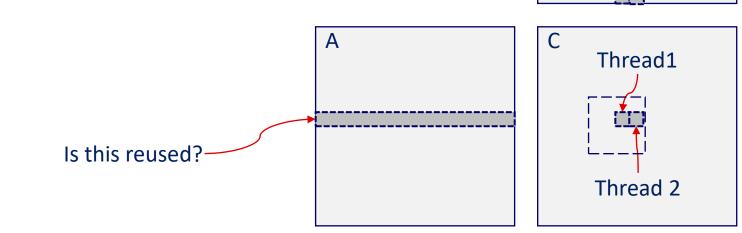

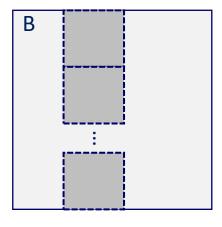

### **CUDA Execution Abstraction**

#### Block: Multi-dimensional array of threads

- o 1D, 2D, or 3D

- $\circ~$  Threads in a block can synchronize among themselves

- $\circ~$  Threads in a block can access shared memory

- CUDA (Thread, Block) ~= OpenCL (Work item, Work group)

- Grid: Multi-dimensional array of blocks

- $\circ$  1D or 2D

- Blocks in a grid can run in parallel, or sequentially

- □ Kernel execution issued in grid units

- □ No/Limited recursion (statically limited recursion depth, at all)

# Simple CUDA Example

# Simple CUDA Example

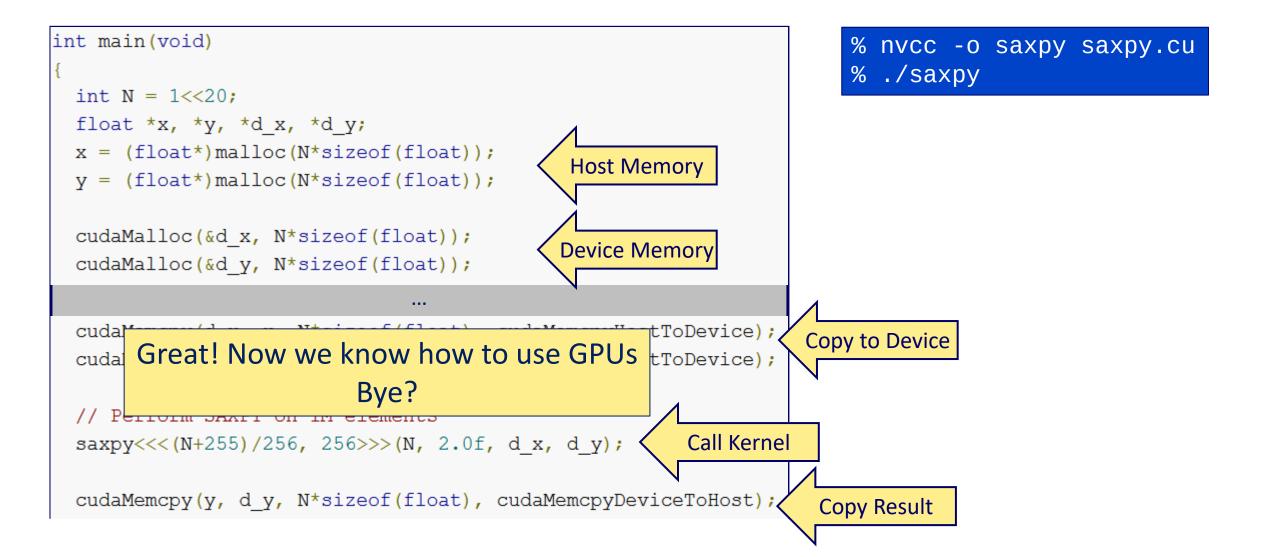

#### End-to-End Example: SAXPY

□ "Single-precision A\*X Plus Y"

```

__global___

void saxpy(int n, float a, float *x, float *y)

{

int i = blockIdx.x*blockDim.x + threadIdx.x;

if (i < n) y[i] = a*x[i] + y[i];

}

```

#### End-to-End Example: SAXPY

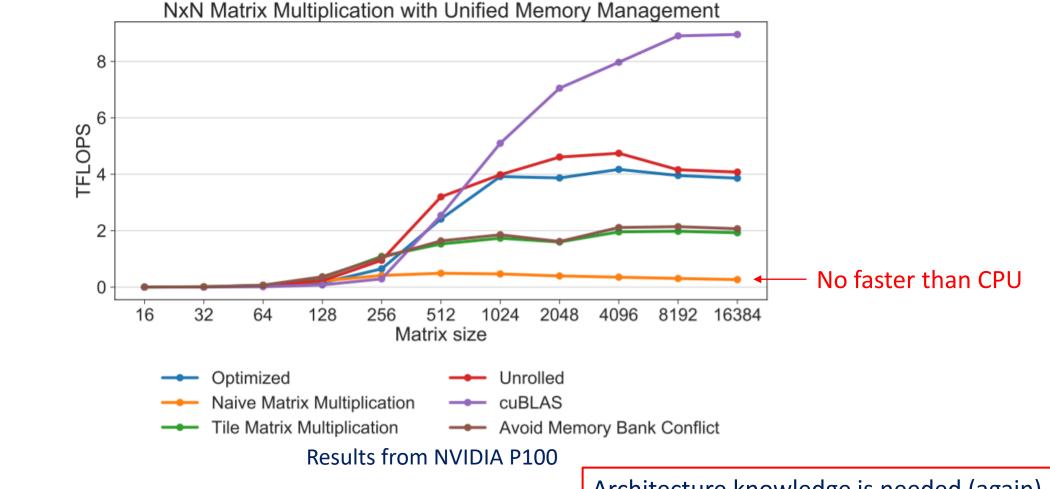

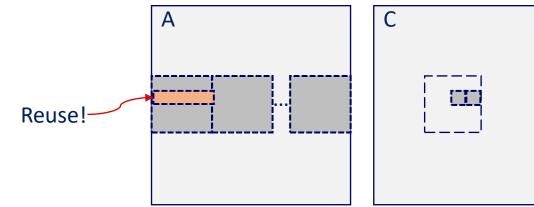

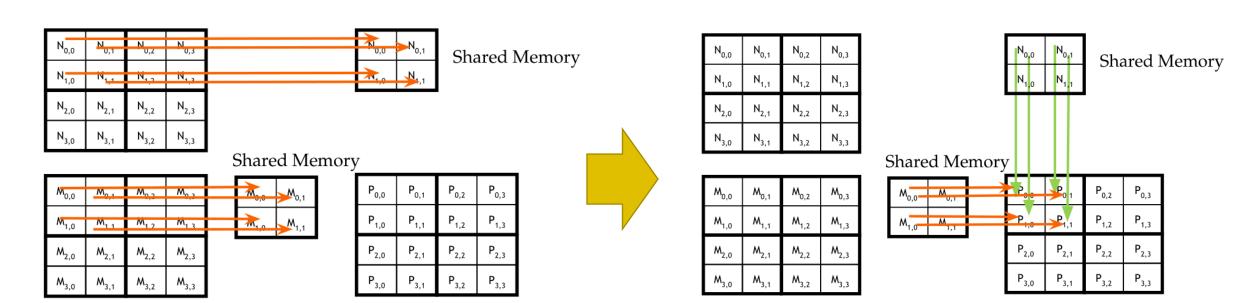

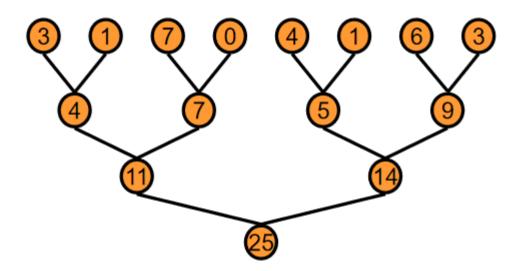

### Matrix Multiplication Performance Engineering

Coleman et. al., "Efficient CUDA," 2017

Architecture knowledge is needed (again)

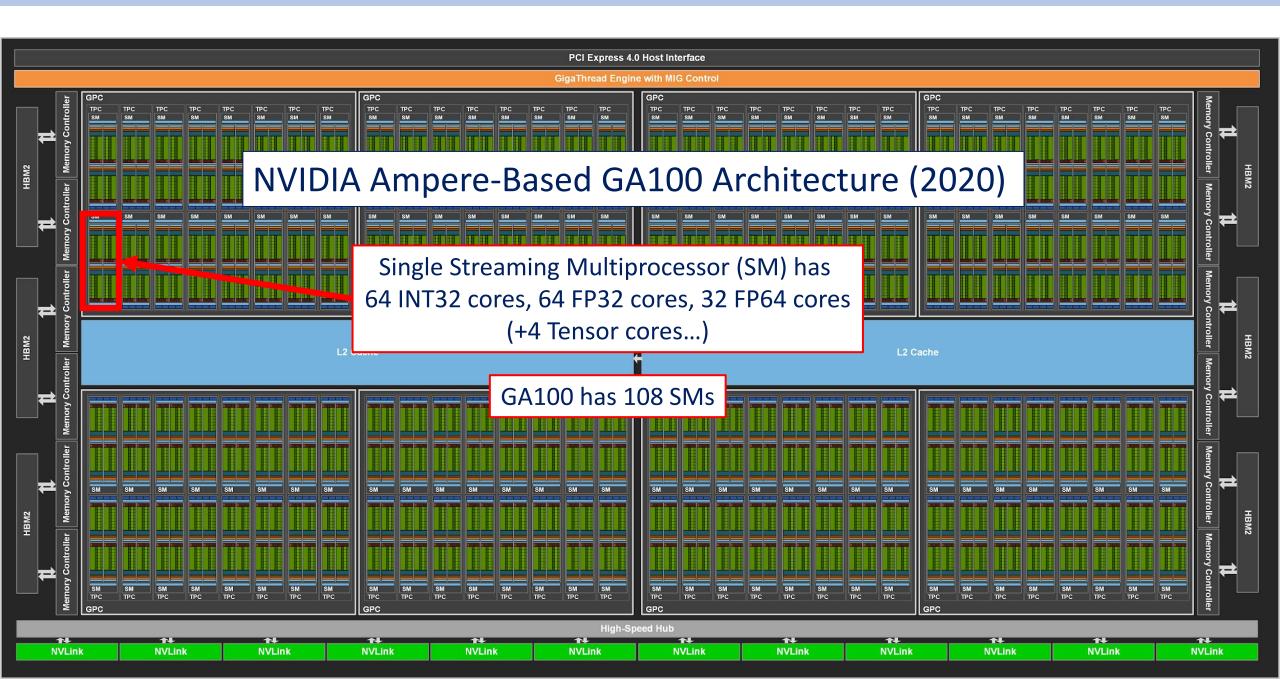

### **Ampere Execution Architecture**

- G4 INT32, 64 FP32, 32 FP64, 4 Tensor Cores

- Specialization to make use of chip space...?

- Not much on-chip memory per thread

- $\circ$  164 KB Shared memory

- o 256 Registers

- □ Hard limit on compute management

- 32 blocks AND 2048 threads AND 1024 threads/block

- e.g., 2 blocks with 1024 threads, or 4 blocks with 512 threads

- Enough registers/shared memory for all threads must be available (all context is resident during execution)

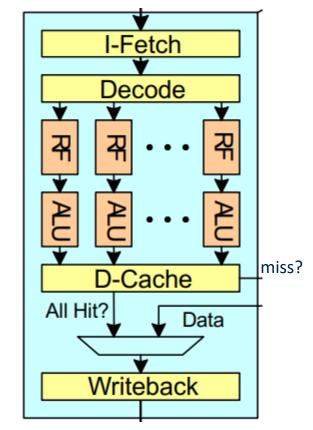

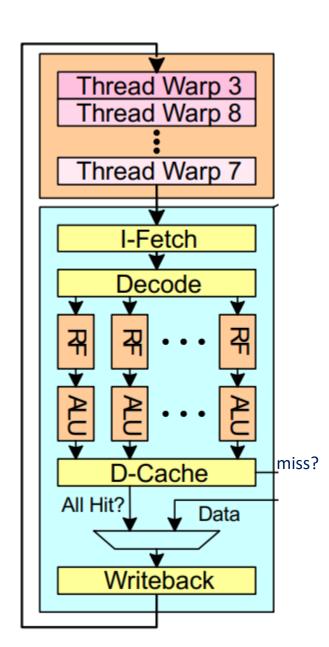

More threads than cores – Threads interleaved to hide memory latency

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L1 Instruc                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                     |                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| L0 Instruction Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   | L0 Instruction Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                     |                                                  |

| Warp Scheduler (32 thread/clk)<br>Dispatch Unit (32 thread/clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   | Warp Scheduler (32 thread/clk)<br>Dispatch Unit (32 thread/clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                     |                                                  |

| Dispatch Offic (32 thread/cik)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                     |                                                  |

| Registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r File (16,38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 x 32-bit)                       | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | File (16,384                                                                                                                                                                                                                                                                                                        | 4 x 32-bit)                                      |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TENSOD CODE                       | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                | TENSOR CORE                                      |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TENSOR CORE                       | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| INT32 INT32 FP32 FP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | INT32 INT32 FP32 FP32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FP64                                                                                                                                                                                                                                                                                                                |                                                  |

| LD/ LD/ LD/ LD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LD/ LD/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                     |                                                  |

| ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ST ST SFU                         | LD/ LD/ LD/ LD/<br>ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LD/ LD/<br>ST ST                                                                                                                                                                                                                                                                                                    | LD/ LD/<br>ST ST SFU                             |

| ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ST ST SFU                         | ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                     | ST ST SFU                                        |

| ST ST ST ST LO<br>Warp S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | st st SFU<br>ache<br>hread/clk)   | ST ST ST ST<br>LO in<br>Warp Sch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ST ST<br>Instruction C<br>Meduler (32 t                                                                                                                                                                                                                                                                             | st st SFU<br>ache<br>hread/clk)                  |

| ST ST ST ST LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | st st SFU<br>ache<br>hread/clk)   | ST ST ST ST<br>LO in<br>Warp Sch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ST ST                                                                                                                                                                                                                                                                                                               | st st SFU<br>ache<br>hread/clk)                  |

| ST ST ST ST LO<br>UUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | st st SPU                         | ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST ST<br>Instruction C<br>Meduler (32 t                                                                                                                                                                                                                                                                             | ache<br>hread/clk)                               |

| ST ST ST ST LO<br>UUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST ST<br>Instruction C<br>cheduler (32 th<br>ch Unit (32 th<br>r File (16,38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | st st SPU                         | ST ST ST ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST ST<br>Instruction C<br>Ineduler (32 th<br>In Unit (32 th                                                                                                                                                                                                                                                         | ache<br>hread/clk)                               |

| st st st st<br>LO<br>Warp S<br>Dispat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ST ST<br>Instruction C<br>theduler (32 th<br>ch Unit (32 th<br>r File (16,38<br>2 FP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | st st SPU                         | st st st st<br>L0 In<br>Warp Sch<br>Dispatch<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | st st<br>nstruction C<br>neduler (32 th<br>1 Unit (32 th<br>File (16,384                                                                                                                                                                                                                                            | ache<br>hread/clk)                               |